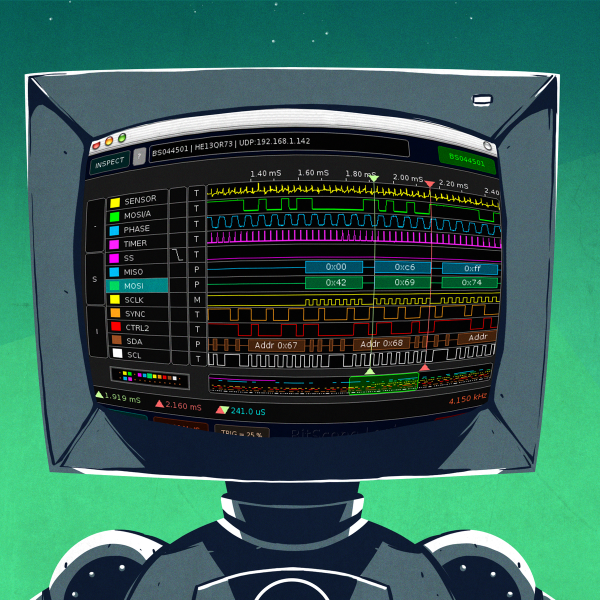

After reading the latest hackit post, [Ben] sent in this older, but simple logic analyzer. The software was written in windows, but the circuit is simple enough, and most hackers I know have more computers than immediate family members. The circuit uses a HC245 octal bus transceiver to feed the 8 data lines on the parallel port. (You can use a variety of chips for this application, most CMOS buffers will probably be fine.)

13 thoughts on “Parallel Port Logic Analyzer”

Leave a Reply

Please be kind and respectful to help make the comments section excellent. (Comment Policy)

In other words, this just connects stuff directly to your parallel port. Should be very easy to make a Linux driver for this. Too bad my printer is parallel… time to upgrade :D

I think it would be nice to add some kind of playback support. Since those pins on the parallel port are bidirectional, it should be simple enough. Time to pull out my soldering iron!

We use freebasic with linux all the time to access the parallel port.

build one of these for your printer:

the hex file works with the 88, 48 and 168 i think. and besides, its well documented

http://www-user.tu-chemnitz.de/~heha/bastelecke/Rund%20um%20den%20PC/USB2LPT/ul-15.htm.en

then you will have a spare lpt port.

I built one of these a few years ago, including linux software: http://uvasux.googlepages.com/simplelogicanalyser

comment i left on the diylife board:

Nice design. I wonder if you get subtle flickers when updating the PWM values. I’ve found in my designs on the 14bit pics, that I have to update the PWM when my ” 1 byte cycle counter” wraps to zero rather than immediately. You are clocking at a higher clock rate (I use 4-8mhz internal clocks with up to 10 PWM channels), so your design may not be so sensitive.

Recently, i’ve given up on the PIC and it’s goofy architecture and moved to the Cypress PSOC parts. They are really neat with dedicated digital and analog blocks. You can set up up to 16 PWM (actually I use pseudo random bit sequences, which have less flicker) outputs, and the C compiler is really reliable vs the buggy stuff i’ve experienced w/ the pic (though the PSOC compiler generates crap code). The PSOC has it’s own shortcomings, such as a really inefficient CPU, but the digital and analog blocks more than make up for it b/c stuff is done in HW vs SW. PSOC is really fun, esp when u wrap your head around it’s way of doing things.

ACK! wrong post. i meant it for the pic rgb color changer. Doh!

This could probably be improved with the addition of an external power source and some high speed opto-couplers,to protect the computer properly.

I used the Fabulous Logic Analyzer for Linux. It uses pretty much the same hardware. This software and hardware combination were in the kits I gave away at Chaos Communication Camp. The software and schematics are available here: http://tfla-01.berlios.de/

This works really well.

I used it last year to view signals from an IR receiver to read the commands that a tv remote control sends out.

Cheers, will build one this weekend. Should last me until I can scrounge the cash for a real one. By the way, anyone have an opinion of analyzers in terms of usb vs standalone?

You might be interested in yet-another-slow-logic analyzer I have created today: http://martin.hinner.info/electronics/piclogix/

The difference between those linked in this article and comments is that mine is standalone, i.e. requires no PC.

i recommend to NOT download or publishing links to poor software like this. I recommend to use an older (2005) but much better, very (!) well documented and designed GNU licenced logic analyzer software from http://tfla-01.berlios.de/.

the software presented in this post is buggy, windows only whitout the possibility of capturing more than “one file line” length (save a captured stream and have a look at it from text editor), able to trigger on one channel.

tfla-01 from berlios was written in 2005, is open source, multiplatform (QT GUI, qt guis are much more comfortable than a few years ago), able to trigger every channel and ABLE to capture for a longer period than just 40ms (24 hours), allowing analysis of command/signalling sequences longer than 40ms.

no, i am not the author of this software, i just needed an lpt capture programm capable to capture data for more than 40ms.

yes, i know that this hackaday article is listed before tfla whit terms concerning this theme.

and no, not only because “the fabulous logic analyzer” is open source i am not interest in

counsel the author about search engine optimisation.

hey guyz.am a final year student in kenya with a project for implementing a pc based logic analyser.unfortunately i happen to have no idea on how to start plus your outlines(basic as they seem to you)are a bit harder for me to comprehend.any help for me pleassseee?